Abdullah Giray Yağlıkçı

I am a tenure-track faculty, leading the Secure and Sustainable System Scaling Lab at Helmholtz Institute Center of Information Security (CISPA). My current research aims enabling secure and sustainable system scaling as chips get denser and many users share chips. We push the boundaries of secure and sustainable system scaling via conducting research on high-performance, energy-efficient, and secure computer architectures and systems.

Join the team! We are always looking for self-motivated people. Please fill out this application form to join us.

Selected Publications

-

"ColumnDisturb: Understanding Column-based Read Disturbance in Real DRAM Chips and Implications for Future Systems"in Proceedings of the 58th International Symposium on Microarchitecture (MICRO), Seoul, South Korea, 2025One of the 12 computer architecture papers of 2025 selected as Top Picks by IEEE Micro.

-

"Chronus: Understanding and Securing the Cutting-Edge Industry Solutions to DRAM Read Disturbance"in Proceedings of the 31st International Symposium on High-Performance Computer Architecture (HPCA), Las Vegas, NV, USA, 2025Full Paper: [ pdf ] Slides: [ ppt ] [ pdf ] Artifact: [ code ] DRAMSec'24 Version: [ Paper ] [ Slides ppt ] [ Slides pdf ]Officially artifact evaluated as available, functional, and reproduced.Invited Talk at Future of Memory Systems (FMS) 2025Invited Talk at Hardwear.io, Amsterdam, 2025

-

"Understanding RowHammer Under Reduced Refresh Latency: Experimental Analysis of Real DRAM Chips and Implications on Future Solutions"in Proceedings of the 31st International Symposium on High-Performance Computer Architecture (HPCA), Las Vegas, NV, USA, 2025Officially artifact evaluated as available, functional, and reproduced.Distinguished Artifact Award at HPCA 2025

-

"BreakHammer: Enhancing RowHammer Mitigations by Carefully Throttling Suspect Threads"in Proceedings of the 57th International Symposium on Microarchitecture (MICRO), Austin, TX, USA, 2024Officially artifact evaluated as available, functional, and reproduced.Invited Talk at Hardwear.io, Amsterdam, 2025

-

"ABACuS: All-Bank Activation Counters for Scalable and Low Overhead RowHammer Mitigation"in Proceedings of the 33rd USENIX Security Symposium (USENIX Security, Philadelphia, PA, USA, 2024Officially artifact evaluated as available, functional, and reproduced.

-

"Spatial Variation-Aware Read Disturbance Defenses: Experimental Analysis of Real DRAM Chips and Implications on Future Solutions"in Proceedings of the 30th IEEE International Symposium on High-Performance Computer Architecture (HPCA), Edinburgh, United Kingdom, 2024

-

"Understanding RowHammer Under Reduced Wordline Voltage: An Experimental Study Using Real DRAM Devices"in Proceedings of the 52nd Annual IEEE/IFIP International Conference on Dependable Systems and Networks (DSN), Baltimore, MD, USA, 2022

-

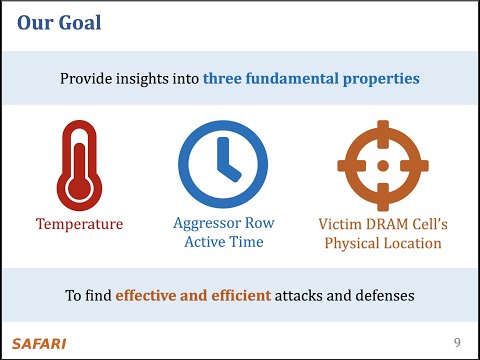

"A Deeper Look into RowHammer's Sensitivities: Experimental Analysis of Real DRAM Chips and Implications on Future Attacks and Defenses"in Proceedings of the 54th International Symposium on Microarchitecture (MICRO), Virtual, 2021

-

"BlockHammer: Preventing RowHammer at Low Cost by Blacklisting Rapidly-Accessed DRAM Rows"in Proceedings of the 27th IEEE International Symposium on High-Performance Computer Architecture (HPCA), Virtual, 2021Paper: [ pdf ] Short Talk (7 mins): [ video ] [ ppt ] [ pdf ] Full Talk (22 mins): [ video ] [ ppt ] [ pdf ] Intel HWSec Academic Awards Talk (2 mins): [ video ] [ ppt ] [ pdf ]Intel Hardware Security Academic Award Finalist (one of 4 finalists out of 34 nominations)

PhD Dissertation

-

"Enabling Efficient and Scalable DRAM Read Disturbance Mitigation via New Experimental Insights into Modern DRAM Chips"PhD Thesis, ETH Zürich, 2024ACM SIGMICRO Dissertation Award 2025IEEE/IFIP DSN W. C. Carter Doctoral Dissertation Award 2025ACM SIGARCH Outstanding Dissertation Award (Honorable Mention) 2025IEEE TTTC McCluskey Doctoral Dissertation Award (Semifinalist) 2025ETH Medal for Outstanding Doctoral Thesis (Nominated) 2024HOST Best Dissertation Award (Finalist) 2024

Selected Talks and Lectures

Lecture in EFCL Summer School

Memory Latency, Data Retention, and Refresh

90 mins |

Video: |

Slides:

Lecture in ETH Zurich

DRAM Robustness and RowHammer Lecture (Second half of the lecture)

1 hour |

Video: |

Slides:

SAFARI Live Seminar

A Deeper Look into RowHammer's Characteristics in Real Modern DRAM Chips

1 hour 50 mins |

Video: |

Slides:

SAFARI Live Seminar

Efficiently and Scalably Mitigating RowHammer in DRAM-Based Memory Systems

2 hours 4 mins |

Video: |

Slides:

Awards & Honors

- ACM SIGMICRO Dissertation Award, 2025 - Recipient

- W. C. Carter PhD Dissertation Award in Dependability, 2025 - Recipient

- ACM SIGARCH / IEEE CS TCCA Outstanding Dissertation Award, 2025 - Honorable Mention

- ETH Medal, 2024 - Nominated

- HOST PhD Dissertation Competition, 2024 - Finalist

- IEEE TTTC E. J. McCluskey Best Doctoral Thesis Award, 2025 - Semi-finalist

- ACM PACT Student Research Competition, 2023 - Recipient for an early version of Svärd (HPCA 2024)

- Intel Hardware Security Academic Award, 2022 - Finalist for BlockHammer (HPCA 2021)

- ISCA Hall of Fame, 2025 - Inducted with 8 papers

- HPCA Hall of Fame, 2025 - Inducted with 10 papers

Employment

Education

Service

Program Committee Member for HPCA, DSN, ISCA, ISMM, and MICRO

Program Committee Member for DRAMSec Workshop at ISCA

Submission and Web Co-Chair for DRAMSec Workshop at ISCA

Reviewer for IEEE CAL

Organization Chair for SaLWo: SAFARI Live Workshop

Artifact Evaluation Committee Member for ASPLOS and DSN

Student Assistant to PC chairs for DSN

External Program Committee Member for DSN

Reviewer for TODAES

Subreviewer for ASPLOS, DSN, ISCA, CAL, DRAMSec, TC, TCAD, and USENIX ATC

Subreviewer for HPCA, MICRO, TCAD, and USENIX ATC

Subreviewer for DSN, ISCA, MICRO, CCS, ISCAS, ISPASS, NVMW, and TCSI

Subreviewer for DSN, ISCA, MICRO, MSST, TCAD, and TED

Subreviewer for ASPLOS, HPCA, PACT, Nature Electronics, TC, and TVLSI

Subreviewer for DSN, MICRO, ISCA, and PLDI

Other Publications

-

"Cleaning up the Mess: Re-evaluating the Real-System Modeling Accuracy of Ramulator 2.0"in Proceedings of the IEEE International Symposium on Performance Analysis of System and Software (ISPASS), Seoul, South Korea, 2026Preprint: [ pdf ]

-

"Memory Band-Aid: A Principled RowHammer Defense-in-Depth"in Proceedings of the Network and Distributed System Security Symposium (NDSS), San Diego, CA, USA, 2026Preprint: [ pdf ]

-

"Revisiting Main Memory-Based Covert and Side Channel Attacks in the Context of Processing-in-Memory"in Proceedings of the 55th Annual IEEE/IFIP International Conference on Dependable Systems and Networks (DSN), Naples, Italy, 2025Officially artifact evaluated as available, reviewed, and reproduced.

-

"Rethinking the Producer-Consumer Relationship in Modern DRAM-Based Systems"IEEE Access, 2024

-

"Sectored DRAM: A Practical Energy-Efficient and High-Performance Fine-Grained DRAM Architecture"ACM Transactions on Architecture and Code Optimization (TACO), 2024

-

"RowPress Vulnerability in Modern DRAM Chips"Special Issue, IEEE Micro, Special Issue: Micro's Top Picks from 2023 Computer Architecture Conferences (MICRO TOP PICKS), 2024Full Paper: [ pdf ]

-

"Read Disturbance in High Bandwidth Memory: A Detailed Experimental Study on HBM2 DRAM Chips"in Proceedings of the 54th Annual IEEE/IFIP International Conference on Dependable Systems and Networks (DSN), Brisbane, Australia, 2024Officially artifact evaluated as both code and dataset available, reviewed and reproducible.

-

"Simultaneous Many-Row Activation in Off-the-Shelf DRAM Chips: Experimental Characterization and Analysis"in Proceedings of the 54th Annual IEEE/IFIP International Conference on Dependable Systems and Networks (DSN), Brisbane, Australia, 2024Officially artifact evaluated as both code and dataset available, reviewed and reproducible.

-

"An Experimental Characterization of Combined RowHammer and RowPress Read Disturbance in Modern DRAM Chips"in Proceedings of the 54th Annual IEEE/IFIP International Conference on Dependable Systems and Networks Disrupt Track (DSN Disrupt), Brisbane, Australia, 2024

-

"CoMeT: Count-Min-Sketch-based Row Tracking to Mitigate RowHammer at Low Cost"in Proceedings of the 30th International Symposium on High-Performance Computer Architecture (HPCA), Edinburgh, UK, 2024Officially artifact evaluated as available, functional, and reproduced.

-

"MIMDRAM: An End-to-End Processing-Using-DRAM System for High-Throughput, Energy-Efficient and Programmer-Transparent Multiple-Instruction Multiple-Data Computing"in Proceedings of the 30th International Symposium on High-Performance Computer Architecture (HPCA), Edinburgh, UK, 2024

-

"SpyHammer: Understanding and Exploiting RowHammer Under Fine-Grained Temperature Variations"IEEE Access, 2024Full Paper: [ pdf ]

-

"RowPress: Amplifying Read Disturbance in Modern DRAM Chips"in Proceedings of the 50th International Symposium on Computer Architecture (ISCA), Orlando, FL, USA, 2023Full Paper: [ pdf ] Extended Version: [ pdf ] Lightning Talk (3 mins): [ video ] [ ppt ] [ pdf ] Full Talk (26 mins): [ video ] [ ppt ] [ pdf ] Source Code: [ code ]Officially artifact evaluated as available, reusable and reproducible.Distinguished artifact award at ISCA 2023.One of the 12 computer architecture papers of 2023 selected as Top Picks by IEEE Micro.

-

"QUAC-TRNG: High-Throughput True Random Number Generation Using Quadruple Row Activation in Commodity DRAM Chips"in Proceedings of the 48th International Symposium on Computer Architecture (ISCA), Virtual, 2021

-

"Revisiting RowHammer: An Experimental Analysis of Modern Devices and Mitigation Techniques"in Proceedings of the 47th International Symposium on Computer Architecture (ISCA), Valencia, Spain, 2020

-

"EDEN: Energy-Efficient, High-Performance Neural Network Inference Using Approximate DRAM"in Proceedings of the 52nd International Symposium on Microarchitecture (MICRO), Columbus, OH, USA, 2019

-

"CROW: A Low-Cost Substrate for Improving DRAM Performance, Energy Efficiency, and Reliability"in Proceedings of the 46th International Symposium on Computer Architecture (ISCA), Phoenix, AZ, USA, 2019

-

"What Your DRAM Power Models Are Not Telling You: Lessons from a Detailed Experimental Study"in Proceedings of the ACM International Conference on Measurement and Modeling of Computer Systems (SIGMETRICS), Irvine, CA, USA, 2018

-

"Understanding Reduced-Voltage Operation in Modern DRAM Devices: Experimental Characterization, Analysis, and Mechanisms"in Proceedings of the ACM International Conference on Measurement and Modeling of Computer Systems (SIGMETRICS), Urbana-Champaign, IL, USA, 2017

Technical Reports

-

"Security Analysis of the Silver Bullet Technique for RowHammer Prevention"arXiv:2106.07084 [cs.CR], 2021Full Paper: [ pdf ]

Publication Venues:

International Symposium on High-Performance Computer Architecture (HPCA): 10 papers International Symposium on Computer Architecture (ISCA): 8 papers International Symposium on Microarchitecture (MICRO): 7 papers IEEE/IFIP International Conference on Dependable Systems and Networks (DSN): 4 papers IEEE/IFIP International Conference on Dependable Systems and Networks Disrupt Track (DSN Disrupt): 2 papers ACM International Conference on Measurement and Modeling of Computer Systems (SIGMETRICS): 2 papers IEEE VLSI Test Symposium (VTS): 1 papers Asia and South Pacific Design Automation Conference (ASP-DAC): 1 papers USENIX Security Symposium: 1 papers Network and Distributed System Security Symposium (NDSS): 1 papers Workshop on DRAM Security (DRAMsec): 1 papersRecent Collaborators

Onur Mutlu Ataberk Olgun Haocong Luo F. Nisa Bostancı İsmail Emir Yüksel Yahya Can Tuğrul Geraldo F. Oliveira Mohammad Sadrosadati Jeremie S. Kim Minesh Patel Oğuz Ergin Hasan Hassan Lois Orosa Oğuzhan Canpolat Juan Gómez-Luna Konstantinos Kanellopoulos Steve Rhyner Jisung Park Saugata Ghose Behzad Salami Jawad Haj-Yahya Joel Lindegger M. Banu Cavlak Majd Osseiran Melina Soysal Taha Shahroodi Abdullah Giray Yaglikci Aditya Manglik Akash Sood Ataberk Olgun Carina Fiedler Daniel Gruss Efraim Rotem Fabrice Devaux Florian Adamsky Geraldo Francisco de Oliveira Hannes Weissteiner Haocong Luo Ivan Puddu Joaquin Olivares Jonas Juffinger Kangqi Chen Kaveh Razavi Maria Makeenkova Martin Heckel Mayank Kabra Mohammed Alser Nandita Vijaykumar Nika Mansouri Ghiasi Nisa Bostanci Onur Mutlu Patrick Jattke Rahul Bera Roknoddin Azizi Sudheendra Raghav Neela Ulrich Ruhrmair Yanos Sazeides Yuxin Guo Zülal Bingol